14/03/2025

In the intricate world of digital design, where the demand for higher performance and seamless data flow is ever-growing, understanding the underlying communication protocols is paramount. One such cornerstone is the Advanced eXtensible Interface, or AXI, a widely adopted standard for high-speed communication within System-on-Chip (SoC) designs. Beyond just defining an interface, the practical application and implementation of AXI, alongside other critical data transport mechanisms, often rely on robust and well-engineered libraries. This article delves into the specifics of the AXI interface and introduces a groundbreaking resource for digital engineers: the Taxi Transport Library. It’s important to clarify from the outset that “Taxi” in this context refers to a sophisticated System Verilog library, not a mode of urban transport, designed to streamline and enhance data handling in complex hardware projects.

- What Exactly is the AXI Interface?

- Introducing the Taxi Transport Library

- Key Components and Capabilities

- Why Choose the Taxi Transport Library for Your Projects?

- Licensing and Community Contributions

- Practical Applications and Example Designs

- Verification and Testing Methodologies

- Comparative Overview: AXI Interface Variants

- Frequently Asked Questions (FAQs)

- Is "Taxi" in "Taxi Transport Library" related to public transportation vehicles?

- What is System Verilog and why is it used in the Taxi Transport Library?

- What is an FPGA and how does the Taxi Transport Library relate to it?

- What is the primary difference between AXI and AXI Stream?

- Can I use the Taxi Transport Library for commercial product development?

- How can I contribute to the development of the Taxi Transport Library?

What Exactly is the AXI Interface?

The AXI (Advanced eXtensible Interface) is a key component of ARM's AMBA (Advanced Microcontroller Bus Architecture) specification, specifically designed to address the high-performance communication needs of modern System-on-Chip (SoC) designs. It provides a standardised way for different intellectual property (IP) blocks within an SoC to communicate efficiently. Imagine an SoC as a bustling city, and AXI as its sophisticated network of motorways and expressways, ensuring that data packets travel swiftly and reliably between various districts (IP blocks).

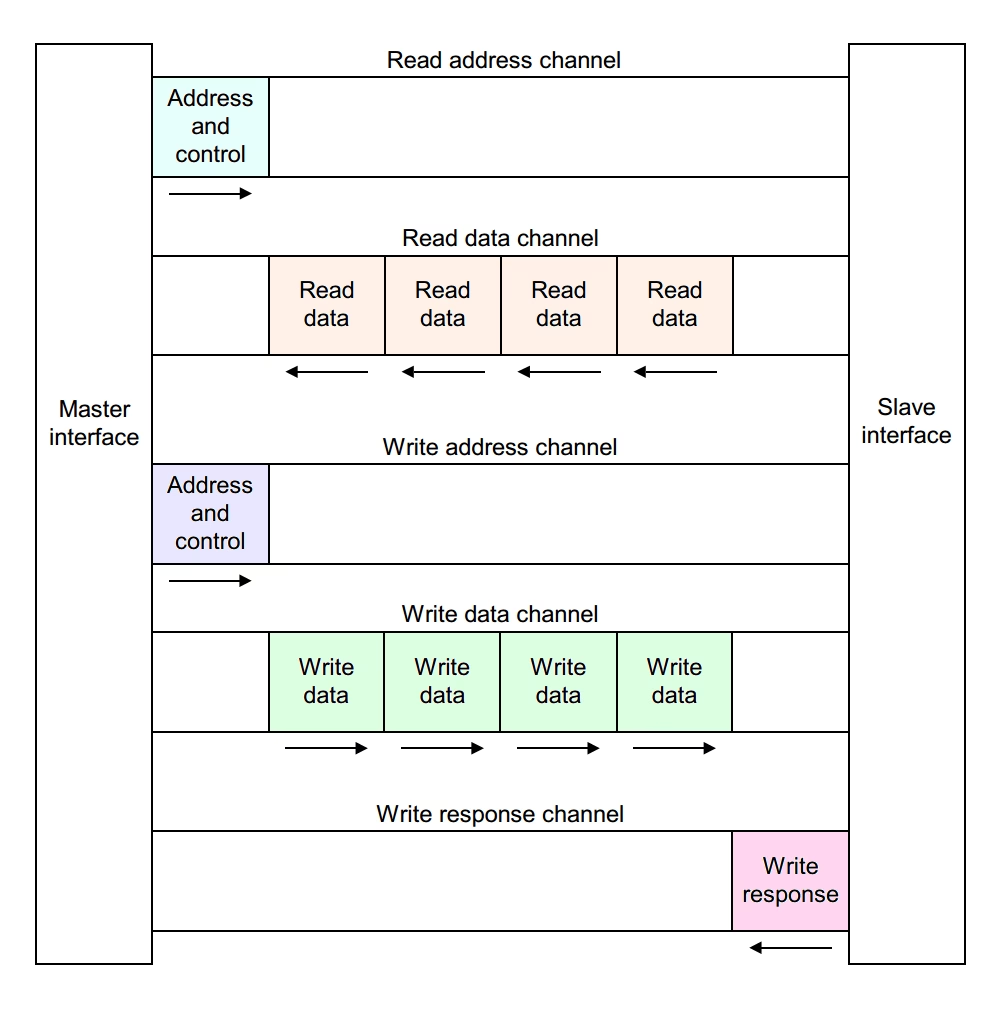

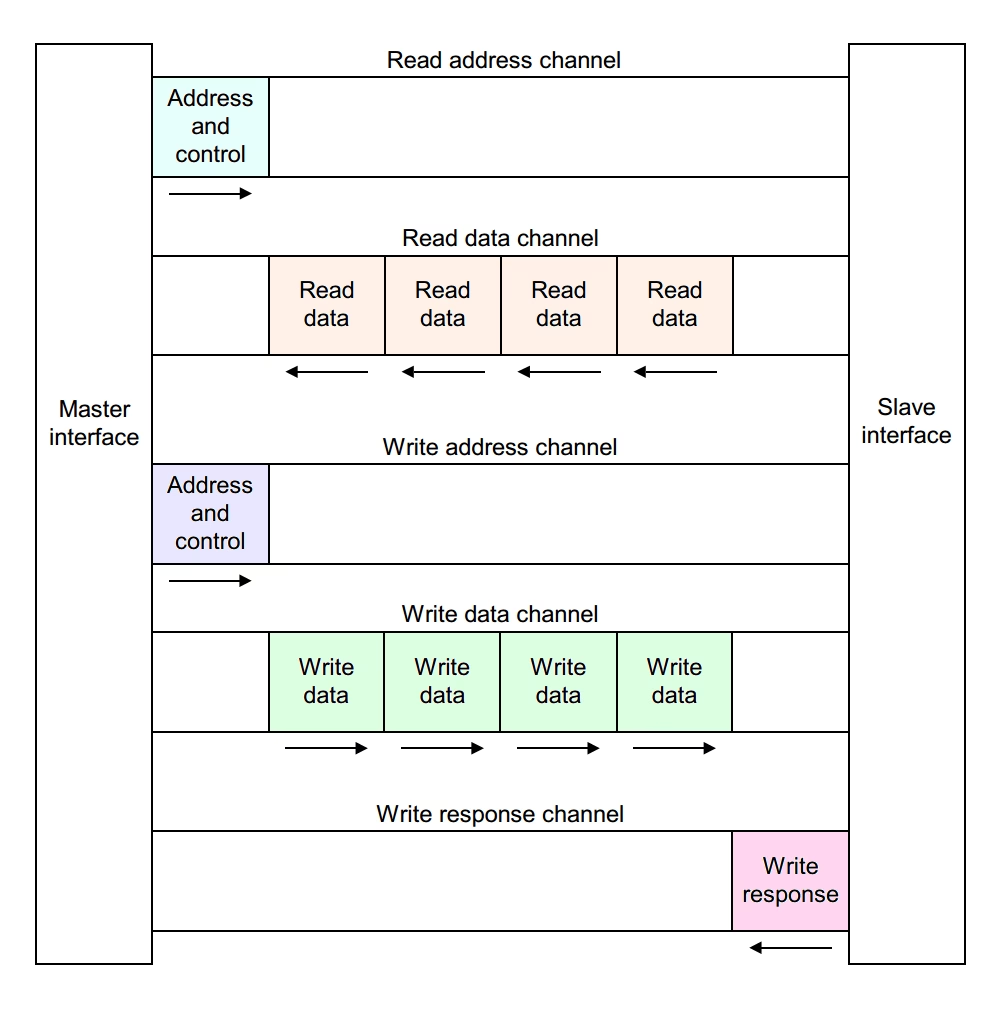

At its core, AXI defines the interface between a master and a slave, a master and an interconnect, and a slave and an interconnect. In essence, a 'master' initiates transactions (like a CPU requesting data), and a 'slave' responds to them (like a memory controller providing data). The 'interconnect' acts as the central hub, routing transactions between multiple masters and slaves, much like a complex junction directing traffic.

Key features that make AXI exceptionally powerful include:

- Separate Channels: AXI employs five independent channels for read address, read data, write address, write data, and write response. This separation allows for parallel operation, significantly boosting throughput. For instance, a master can issue a new read address while waiting for data from a previous read, or perform reads and writes concurrently.

- Burst-Based Transactions: Data is transferred in bursts, meaning a single address phase can be followed by multiple data transfers. This is highly efficient for accessing contiguous memory locations, as it reduces the overhead associated with repeated address phases.

- Out-of-Order Completion: AXI allows transactions to complete in a different order from which they were issued, provided data dependencies are respected. This flexibility, coupled with transaction IDs, helps in maximising bus utilisation and overall performance.

- Multiple Outstanding Transactions: A master can issue multiple transactions without waiting for the previous one to complete. This pipelining capability further enhances throughput, especially in systems with varying latencies.

- Unaligned Data Transfers: AXI supports unaligned data transfers, providing flexibility in how data is accessed and stored.

Variations of AXI

The AXI specification encompasses several variations tailored for different applications:

- AXI (Full AXI): This is the high-performance version, suitable for high-bandwidth applications like memory controllers or direct memory access (DMA) engines. It supports all the advanced features mentioned above.

- AXI-Lite: A simplified version of AXI, designed for low-throughput, single-transaction communication, often used for register access or control paths. It lacks burst support and has a simpler handshake mechanism, making it easier to implement for less complex peripherals.

- AXI Stream: Unlike AXI and AXI-Lite, AXI Stream is designed for unidirectional data transfer without address information. It's ideal for streaming applications where data flows continuously, such as video processing pipelines or network packet processing. It uses a simple VALID/READY handshake protocol.

Understanding these distinctions is crucial for digital designers to select the appropriate interface for their specific needs, ensuring optimal resource utilisation and performance.

Introducing the Taxi Transport Library

While the AXI specification provides the blueprint for communication, implementing it effectively in hardware description languages like System Verilog can be a complex and time-consuming task. This is where the Taxi Transport Library, developed by FPGA Ninja, LLC, steps in. The goal of this innovative library is to provide a comprehensive set of performant, easy-to-use building blocks in modern System Verilog, specifically designed to facilitate robust data transport and interfacing.

The library addresses both internal communication within an FPGA or ASIC via AXI and AXI Stream, and external interfacing through widely used protocols such as Ethernet, PCI Express (PCIe), UART, and I2C. By offering pre-verified, high-quality components, Taxi aims to significantly reduce development time and effort, allowing engineers to focus on the unique aspects of their designs rather than re-implementing standard communication interfaces.

Each building block within the Taxi library is accompanied by thorough testbenches and simulation models, leveraging powerful verification frameworks like Cocotb and Verilator. This commitment to robust testing ensures the reliability and correctness of the components, instilling confidence in their use for critical applications. The library is also under active development, promising continuous improvements and the addition of new components over time to meet evolving industry needs.

Key Components and Capabilities

The Taxi Transport Library boasts an impressive array of components, categorised by their primary function. This modular approach allows designers to pick and choose exactly what they need, building complex systems from reliable, pre-tested parts.

AXI and AXI Lite Interfaces

These components provide the fundamental building blocks for AXI-compliant systems:

- AXI SV interface: Core System Verilog interface for full AXI.

- AXI Register slice: For pipelining AXI signals to improve timing.

- Single-port RAM: Simple memory block accessible via AXI.

- AXI lite SV interface: System Verilog interface for the simpler AXI-Lite protocol.

- AXI lite Register slice: Pipelining for AXI-Lite.

- Dual-port RAM: Memory accessible by two independent AXI-Lite masters.

AXI Stream Components

Designed for high-throughput streaming applications, these components facilitate efficient data flow:

- AXI stream SV interface: The core interface for streaming data.

- AXI stream Register slice: For pipelining AXI Stream signals.

- Width converter: Adapts data bus width between different stream components.

- Synchronous FIFO: First-In, First-Out buffer for same-clock domain streaming.

- Asynchronous FIFO: FIFO for streaming data across different clock domains.

- Combined FIFO + width converter: Integrated solutions for complex data path needs.

- Multiplexer/Demultiplexer/Broadcaster/Concatenator/Switch: For routing and combining/splitting data streams.

- COBS encoder/decoder: Consistent Overhead Byte Stuffing for robust data framing.

- Pipeline register/FIFO: General-purpose pipelining and buffering for stream data.

Ethernet MACs and PHY Interfaces

Enabling high-speed networking capabilities:

- 10/100 MII MAC / + FIFO: Media Independent Interface (MII) for Fast Ethernet.

- 10/100/1000 GMII MAC / + FIFO: Gigabit Media Independent Interface (GMII) for Gigabit Ethernet.

- 10/100/1000 RGMII MAC / + FIFO: Reduced Gigabit Media Independent Interface (RGMII) for Gigabit Ethernet.

- 1G MAC / + FIFO: Dedicated 1 Gigabit Ethernet MAC.

- 10G/25G MAC / + FIFO: High-speed MACs for 10 Gigabit and 25 Gigabit Ethernet.

- 10G/25G MAC/PHY / + FIFO: Integrated MAC and PHY (Physical Layer) components for ultra-high-speed networking.

- MII/GMII/RGMII PHY interface: Components for connecting to external PHY devices.

- 10G/25G MAC/PHY/GT wrapper for UltraScale/UltraScale+: Specific wrappers for Xilinx UltraScale/UltraScale+ devices.

General Input/Output and Utility Components

Essential for basic hardware interaction and data manipulation:

- Switch debouncer: Eliminates spurious signals from mechanical switches.

- LED shift register driver: For controlling LED displays.

- Generic IDDR/ODDR: Input/Output Double Data Rate registers.

- Source-synchronous DDR/SDR input/output (differential/single-ended): For precise high-speed I/O.

- Linear-feedback shift register (LFSR)/CRC modules: For pseudo-random bit generation, data scrambling, and error checking.

- PRBS generator/checker: Pseudo-Random Binary Sequence for testing high-speed links.

Low-Speed Serial Interfaces

For communication with a wide range of peripherals:

- I2C master/slave/single register: Inter-Integrated Circuit bus components.

- MDIO master: Management Data Input/Output for PHY configuration.

- UART: Universal Asynchronous Receiver-Transmitter for serial communication.

Primitives and Synchronization

Core building blocks and timing utilities:

- Arbiter/Priority encoder: For managing shared resources.

- Reset synchronizer/Signal synchronizer: For safe signal transfer across clock domains.

Precision Time Protocol (PTP) and Statistics

For precise timing and system monitoring:

- PTP clock/CDC/period output/TD leaf clock/TD PHC/TD relative-to-ToD converter: Components for implementing IEEE 1588 Precision Time Protocol.

- Statistics collector/counter: For monitoring system metrics and performance.

Extensible FPGA Control Protocol (XFCP)

A flexible protocol for managing and configuring FPGA designs:

- XFCP UART/AXI/AXI lite/I2C master modules: Interfaces for XFCP via various protocols.

- XFCP switch: For routing XFCP commands.

This comprehensive list underscores the library's commitment to providing a holistic solution for complex digital design challenges, from fundamental data movement to advanced networking and timing.

Why Choose the Taxi Transport Library for Your Projects?

The decision to incorporate an external library into a complex hardware project is significant, and the Taxi Transport Library offers compelling reasons for its adoption:

- High Performance and Reliability: Designed with performance in mind, the components are optimised for high-speed operation, and their accompanying testbenches ensure a high degree of reliability.

- Modern System Verilog: The library is written in modern System Verilog, adhering to best practices and making it easier for contemporary designers to integrate and understand.

- Ease of Use: By providing pre-built, well-documented modules, the library simplifies the integration of complex interfaces, reducing the learning curve and potential for errors.

- Extensive Verification: The use of Cocotb and Verilator for simulation and testing signifies a robust verification methodology, which is critical for hardware development.

- Broad Compatibility: With support for numerous FPGA boards from various vendors (Xilinx, Altera, etc.), and a wide range of interfaces, the library offers significant flexibility.

- Active Development and Support: Being under active development by FPGA Ninja, LLC, users can expect ongoing updates, bug fixes, and new features.

Licensing and Community Contributions

The Taxi Transport Library operates under a dual-license model, offering flexibility while supporting continued development. It is available under either the CERN Open Hardware Licence Version 2 - Strongly Reciprocal (CERN-OHL-S 2.0) or a paid commercial license. This approach encourages an open-source ecosystem while providing options for commercial entities with specific intellectual property requirements.

Under the CERN-OHL-S 2.0, users are required to provide the source code of their entire digital design, including modifications and extensions, upon request, ensuring the design can be rebuilt. This reciprocal nature fosters transparency and collaboration within the hardware design community. For those where this restriction is not suitable for their product, a commercial license is available, allowing for more proprietary development. Licence fees directly contribute to the ongoing development and maintenance of the project, ensuring its longevity and continued improvement.

To maintain the integrity and quality of the project, contributions to the Taxi library are accepted under a contributor license agreement, ensuring clarity on intellectual property rights for all parties involved.

Practical Applications and Example Designs

To demonstrate the practical utility and capabilities of the Taxi Transport Library, a wide array of example designs are provided. These designs target various popular FPGA boards, showcasing how different components of the library can be integrated and utilised in real-world scenarios. From high-end data centre accelerators like Xilinx Alveo boards to more accessible development kits such as the Digilent Arty A7, the library supports a broad spectrum of hardware platforms.

These examples serve as invaluable starting points for new projects, illustrating best practices and providing tested configurations that can be adapted and expanded upon. While building these examples may require specific vendor toolchains and potentially IP licenses, they are essential resources for understanding the library's full potential in diverse applications.

Verification and Testing Methodologies

A crucial aspect of any reliable hardware library is its verification methodology. The Taxi Transport Library places a strong emphasis on robust testing, utilising modern, widely-adopted frameworks. The included testbenches are designed to be run with:

- Cocotb: A Python-based co-simulation framework that allows for writing testbenches in Python, offering flexibility and powerful testing capabilities for Verilog/System Verilog designs.

- Verilator: A free and open-source Verilog/System Verilog simulator that compiles synthesizable Verilog/System Verilog code into C++ or SystemC code, enabling fast simulation.

- Pytest: A popular Python testing framework, used in conjunction with Cocotb-test, to organise and execute the test suites efficiently.

This comprehensive testing strategy ensures that the components are thoroughly validated across various scenarios, contributing significantly to the overall quality and trustworthiness of the library.

Comparative Overview: AXI Interface Variants

To further clarify the distinct roles of the AXI interface variants, here’s a comparative table:

| Feature | AXI (Full) | AXI-Lite | AXI Stream |

|---|---|---|---|

| Purpose | High-performance memory-mapped transactions | Simple register access, control paths | Unidirectional data streaming |

| Channels | 5 (AR, R, AW, W, B) | 5 (AR, R, AW, W, B) | 2 (TVALID, TDATA, TLAST, etc.) |

| Address Phase | Present (burst support) | Present (no burst) | Absent |

| Burst Support | Yes (fixed, incremental, wrapping) | No (single transfers only) | N/A (continuous flow) |

| Data Transfer Direction | Bidirectional (read/write) | Bidirectional (read/write) | Unidirectional |

| Complexity | High | Low | Medium |

| Typical Use Cases | DMA controllers, high-bandwidth peripherals, memory interfaces | Control registers, status registers, simple peripherals | Video processing, network packet handling, DSP pipelines |

Frequently Asked Questions (FAQs)

No, absolutely not. The name "Taxi" in "Taxi Transport Library" is simply a project name chosen by its developers, FPGA Ninja, LLC. It has no association whatsoever with public transportation vehicles. It refers to a library of hardware design components for data transport.

What is System Verilog and why is it used in the Taxi Transport Library?

System Verilog is a powerful hardware description and verification language (HDVL) used for designing and verifying electronic systems, particularly complex digital circuits like those found in FPGAs and ASICs. It builds upon Verilog HDL with advanced features for verification, object-oriented programming, and high-level modelling. The Taxi Transport Library uses modern System Verilog to provide high-quality, synthesizable, and verifiable building blocks for digital designs, making them robust and easy to integrate.

What is an FPGA and how does the Taxi Transport Library relate to it?

FPGA stands for Field-Programmable Gate Array. It's an integrated circuit designed to be configured by a customer or designer after manufacturing. FPGAs are highly flexible and can implement custom digital logic circuits, making them ideal for rapid prototyping, specialised computing, and applications requiring high parallelism. The Taxi Transport Library provides pre-designed and verified IP cores (intellectual property blocks) in System Verilog that can be directly synthesised and implemented onto FPGAs, greatly simplifying the development of complex FPGA-based systems, especially those requiring high-speed data interfaces like AXI, Ethernet, or PCIe.

What is the primary difference between AXI and AXI Stream?

The primary difference lies in their purpose and structure. AXI (and AXI-Lite) are memory-mapped interfaces, meaning they involve address information to read from or write to specific memory locations or registers. They support bidirectional data transfer and burst transactions. AXI Stream, on the other hand, is a streaming interface that focuses solely on unidirectional data flow without any address information. It's designed for continuous, high-throughput data pipelines where data simply flows from a source to a sink, making it ideal for applications like video processing or network data paths.

Can I use the Taxi Transport Library for commercial product development?

Yes, you can. The Taxi Transport Library offers a dual-license model. You can use it under the CERN Open Hardware Licence Version 2 - Strongly Reciprocal (CERN-OHL-S 2.0), which requires you to share the source code of your entire digital design if requested. Alternatively, if this reciprocal licence is not suitable for your commercial product's intellectual property strategy, you can obtain a paid commercial license directly from FPGA Ninja, LLC. This commercial option provides more flexibility regarding proprietary development.

How can I contribute to the development of the Taxi Transport Library?

Contributions to the Taxi Transport Library are welcome. To contribute, you typically need to sign a contributor license agreement (CLA) with FPGA Ninja, LLC. This agreement helps to clarify the intellectual property rights for all contributions and ensures the project can maintain its dual-license model. Details on the contribution process and the CLA would typically be found in the project's documentation or GitHub repository.

In conclusion, the AXI interface stands as a critical standard for high-performance communication in modern digital designs. However, the true power of such standards is unlocked through well-crafted and comprehensive implementation libraries. The Taxi Transport Library emerges as a vital resource for digital engineers, offering a meticulously designed suite of System Verilog components that simplify the complexities of data transport across a multitude of interfaces. By providing tested, performant, and easy-to-use building blocks, it empowers designers to accelerate their FPGA and ASIC projects, focusing on innovation rather than re-inventing the wheel. Whether you're grappling with high-speed Ethernet, intricate AXI transactions, or simple serial communication, the Taxi Transport Library offers a robust and forward-thinking solution.

If you want to read more articles similar to Unravelling AXI and the Taxi Transport Library, you can visit the Taxis category.